CPU设计

WHU《计算机设计实践》课程实验

使用工具:

Rars : risc-v汇编和运行时模拟器

ModelSim

vivado

编程语言:

Verilog

assembly

零基础扫盲

什么是FPGA(Field Programmable Gate Array)?

FPGA,即现场可编程门阵列,是一种可完成通用功能的可编程逻辑芯片,即可以对其进行编程实现某种逻辑处理功能。

FPGA与Verilog

Verilog用于描述和设计数字电路的功能和结构。设计者使用Verilog编写代码,定义电路的行为和连接方式。

编写完成的Verilog代码需要经过综合(Synthesis),转化为门级网表(Netlist),然后进行布局布线(Place and Route),完成布局布线后,所有的逻辑单元和连接将被转化为特定的配置数据,这些数据用于配置FPGA的硬件资源。这些配置数据将会被保存为一个比特流文件(.bit文件),这个文件包含了所有FPGA硬件资源的配置指令,可以在FPGA上加载并执行。

Vivado与ModelSim

Vivado是 集成设计环境

ModelSim 具有强大的仿真功能

参考示例:

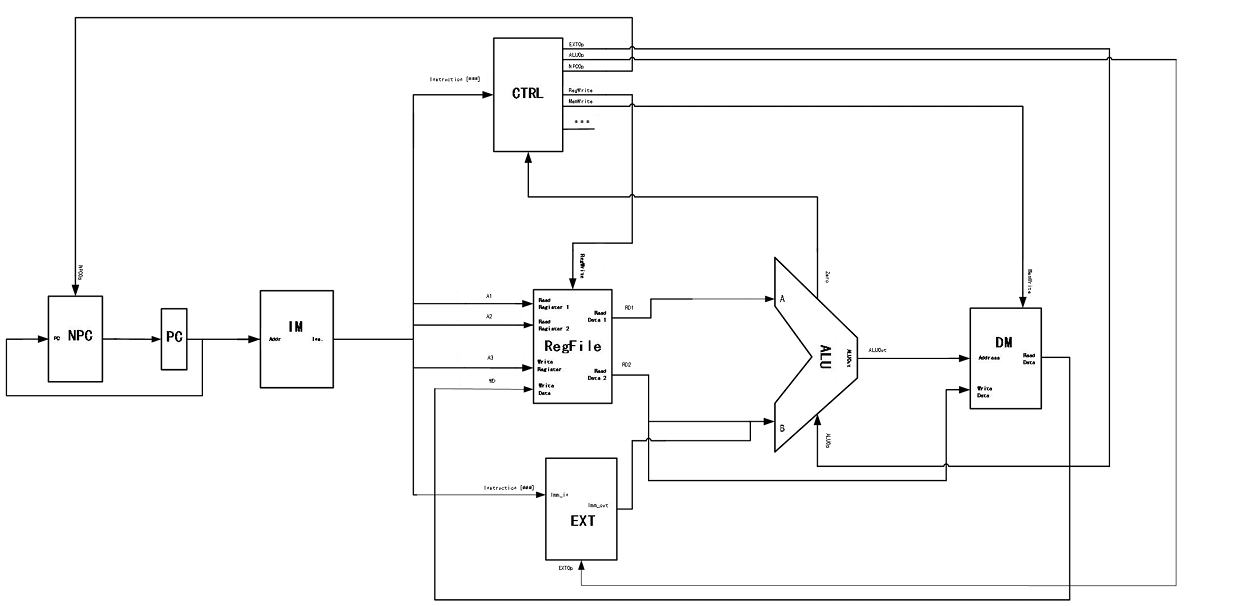

单周期CPU,支持14条指令

- add sub xor or and srl sra sll

- lui addi lw

- sw beq jal

单周期CPU ModelSim 仿真工程SCCPU_SIM

测试代码rv32_sc_sim.dat

流水线CPU,支持12条指令

- add sub xor or and srl sra sll

- lui addi lw

- sw

流水线CPU ModelSim 仿真工程 PLCPU_SIM

测试代码rv32_pl_sim.dat

示例工程及源码

\CODExp\demo\sccpu_sim\project\SCCPU_SIM:实现了14条指令单周期CPU的ModelSim示例工程

\CODExp\demo\sccpu_sim\source\ :目录包含14条指令单周期CPU的ModelSim仿真代码

\CODExp\demo\sccpu_fpga\source\: 目录包含了14条指令单周期CPU的Vivado仿真代码及约束文件(在此基础上可以直接构建Vivado工程)

\CODExp\testcode\demo\目录包含示例单周期CPU和流水线CPU工程的测试代码(asm、dat文件)

\CODExp\testcode\task\目录包含设计目标单周期CPU和流水线CPU工程的测试代码(asm、dat或coe文件)

实验一——单周期CPU

对示例单周期CPU进行指令扩展,至少支持以下指令

add sub xor or and srl sra sll

lui addi lw sw beq jal

==增加指令

slt sltu andi ori xori

srli srai slli slti sltui

bne bge bgeu blt bltu ==

J型指令

jalr

可能出现的问题:

- 文件路径

全英文 - 文件找不到

最好用copy

RARS使用

ModelSim使用

chardet 是一个用于自动检测文本数据编码格式的 Python 库。它可以识别多种字符编码,如 UTF-8、GBK、ISO-8859-1 等,广泛应用于处理不同编码格式的文本数据时,帮助开发者避免乱码问题。

安装:

可以通过 pip 安装 chardet:

bash

1 | |

vscode

如何在VSCode中优雅地书写Verilog_vscode verilog-CSDN博客

ALU单元:

有A口、B口两个输入口接收数据

一个口接收ALUOp操作数

一个C口输出操作结果

一个口输出Zero信号

(用于指示是否是B型指令)

A、B、C都是32位

需要扩充的:

1 | |

过程中遇到的问题:

仿真时忘记关闭允许优化,导致不能add mov(失败)